我们说看到的大部分单片机,基本都实现了内部集成电路(I2C)串行总线接口。I2C对于连接主板或嵌入式系统上的许多低速外设非常有用。这些接口使用7位寻址方案,它允许多个主设备通过简单的2线总线控制多个外设。

在设计PCB时,有时由于总线的物理尺寸变得很大,因此需要缓冲器。I2C缓冲器就像一种中继器,但它并不意味着克服总线上的损耗。由于I2C总线的上升时间通常较慢,因此这些总线不会像高速数字总线那样因损耗而出现信号衰减。相反,它们将时序特性恢复到某个所需的水平,以便可以根据需要使总线的大小更大。

一、I2C总线电气特性

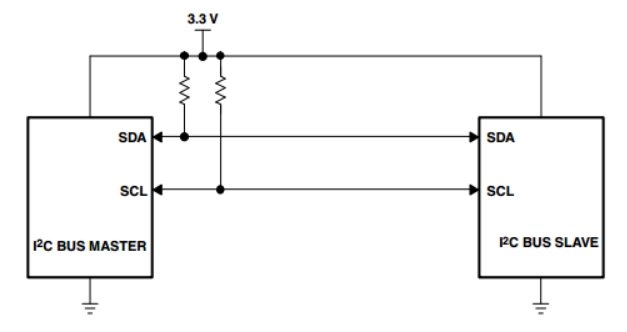

I2C总线由两条活动线组成:串行时钟(SCL)和串行数据(SDA)线。这两条线都连接到主控制器或外围ASIC上的引脚,这两个引脚都是需要上拉电阻的开漏引脚。这意味着主设备或外围设备可以将SDA线拉低,而上拉电阻器被动地将线返回到高电压电平,从而切换所有逻辑状态。

影响I2C总线性能的两个关键电气参数包括:

(1)总线电容(Cbus):SCL和SDA迹线以及连接到总线的设备上的所有输入引脚的电容较高,会增加数据信号和时钟沿的上升时间。

(2)上拉电阻(R):SCL/SDA和VCC之间连接一个电阻。较低的电阻值会缩短上升时间,但会增加流经开漏极的电流(功耗较高)。

I2C总线中上拉电阻的典型值为10 kOhms。例如,如果总总线电容为 100 pF,则SCL/SDA信号的 10%-90%上升时间约为2.2微秒。通过将I2C总线本质上视为充电/放电RC电路,可以轻松计算出这一点。总线如下图所示:

随着越来越多的设备添加到I2C总线,由于每个设备的负载电容和额外的走线电容,Cbus的值也会增加。最终,总电容将降低可以可靠支持的最大I2C时钟速度。较高的总线电容可以用较小的上拉电阻来抵消,但较小的电阻会通过开漏引脚增加功耗。有些漏极电流可能仅限于几毫安,这就是上拉电阻值应在10 kOhms左右的原因。

如果上升时间超过I2C器件的输入阈值区域,缓慢的上升时间也会导致时序问题,这可能会导致接口时序窗口期间电压电平的错误。

为什么要添加I2C缓冲器?

为了说明为什么需要I2C缓冲器,让我们考虑一个例子。假设我们有一块带有两个I2C设备、一个单片机和一个EEPROM的板。单片机充当I2C主设备,EEPROM充当外围设备。

在400 kHz的快速模式时钟速度下,主机可以正确地访问EEPROM中的数据,不会出现时序错误。但如果在板上添加更多外围 IC,总线最终会停止工作。这些额外的设备增加了现有总线的电容。由于这些设备全部并行添加到总线,因此增加的电容开始导致总线上所有设备的上升时间变慢,并最终出现通信错误。

解决I2C总线性能限制的主要方法有几种:

(1)较低的上拉电阻值:使用较小的电阻可缩短上升时间,但会因增加漏极电流而大大增加功耗。

(2)降低I2C时钟速度:这会增加SCL/SDA信号上升沿的时序裕度,但也会降低吞吐量。

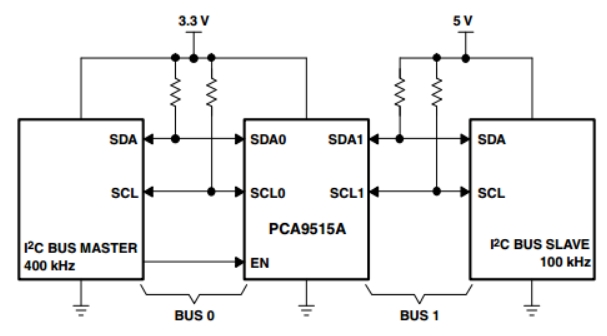

(3)添加I2C缓冲器/中继器:I2C缓冲器将总线分成多个较小的段,这些段可以通过缓冲器独立驱动。

I2C缓冲器及其总线连接的结构如下所示:

二、在PCB设计中实现I2C缓冲器

I2C缓冲器允许工程师将大型总线划分为较小的段,这最大限度地减少了每个部分的电容。通过降低电容,可以增加上拉电阻值以降低I2C功耗,同时仍满足上升时间要求。

I2C缓冲器还可以提供电平转换功能,可在段之间升高或降低信号。这允许高压设备与低压设备通信,但两个电源电压都需要添加到PCB中。

设计PCB时,如果出现以下情况,请考虑添加I2C缓冲器或中继器:

(1)I2C总线具有来自许多设备的高电容。

(2)由于上拉电阻较大,SDA/SCL上升时间太慢。

(3)I2C设备需要不同的信号电平。

(4)I2C设备需要不同的时钟频率。

(5)I2C器件具有不同的上拉电阻限制。

(6)总线速度较高时会发生通信错误。

使用I2C缓冲器的一些好处包括:

(1)将大总线分成更小的段以减少电容。

(2)通过最小化每个段上的电阻值来延长上升时间。

(3)与单个长总线相比,可实现更高的I2C时钟速度。

(4)防止传播延迟影响总线时序。

(5)隔离总线段之间的电气噪声。

三、I2C缓冲器的放置位置

当布局具有多个I2C设备的PCB时,有几种有效的方法来放置I2C缓冲器:

(1)将设备集群分成I2C段。如果某些 I2C 设备在电路板上物理分组在一起,则在集群之间放置缓冲器可将它们隔离到单独的总线段中。这包含每组内的电容。

(2)将缓冲器放置在总线中间附近。在长总线的中间放置缓冲器有助于在两个段上均匀地分配电容。这样,缓冲器在总线的每一侧看到/创建相似的上升时间。

(3)在电容非常高的设备附近放置一个缓冲器。如果一些外围设备具有较大的电容,则可以将它们放置在缓冲器的输出侧,这样它们就不会减慢总线的其余部分。

(4)使用多个级联缓冲器来划分复杂的总线。对于在大面积上分布有许多设备的总线,级联2-3个缓冲器将总线分成几个低电容段,以获得更好的性能。

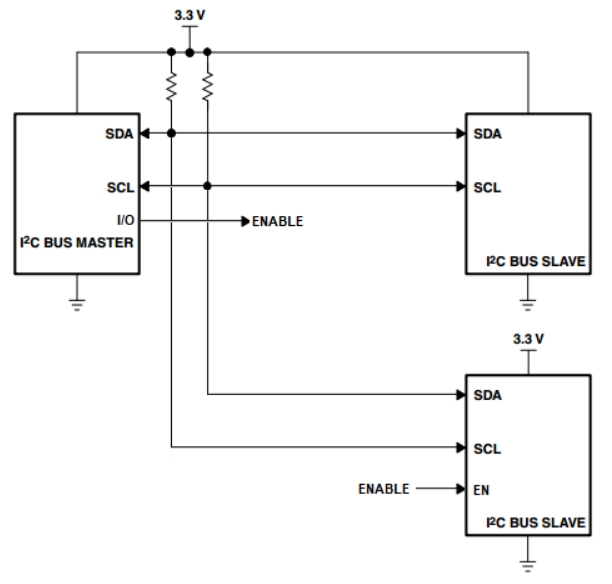

I2C缓冲器作为备份总线

使用 I2C 缓冲器的另一种选择是作为备份总线,这实际上创建了主设备可以通过其进行通信的冗余总线。如果总线上有可能发生故障,则可以启用缓冲器以打开备份组件或外设。这种类型的系统常见于高可靠性应用,例如基础设施或工业系统的电力电子设备。

当设备故障可能导致整个系统瘫痪时,就会使用缓冲器。总线上单个设备的故障可以通过在总线上放置一个用缓冲器分隔的冗余电路来克服。然后可以通过打开其电源或切换其ENABLE/SHDN引脚来启用缓冲器。

在这种情况下,需要一种控制方法来感测受保护设备并确定该设备是否发生故障。如果设备发生故障,主控制器可以通过切换使能引脚切换到受保护的总线。这需要在嵌入式应用中多付出一些功夫,但考虑余量来设计总线可确保系统的长期可靠性。

以上就是英锐恩单片机开发工程师分享的单片机PCB电路设计知识:为I2C总线添加缓冲器。英锐恩专注单片机应用方案设计与开发,提供8位单片机、32位单片机。